昨日予想した内容が早速崩れた。

30%増量か

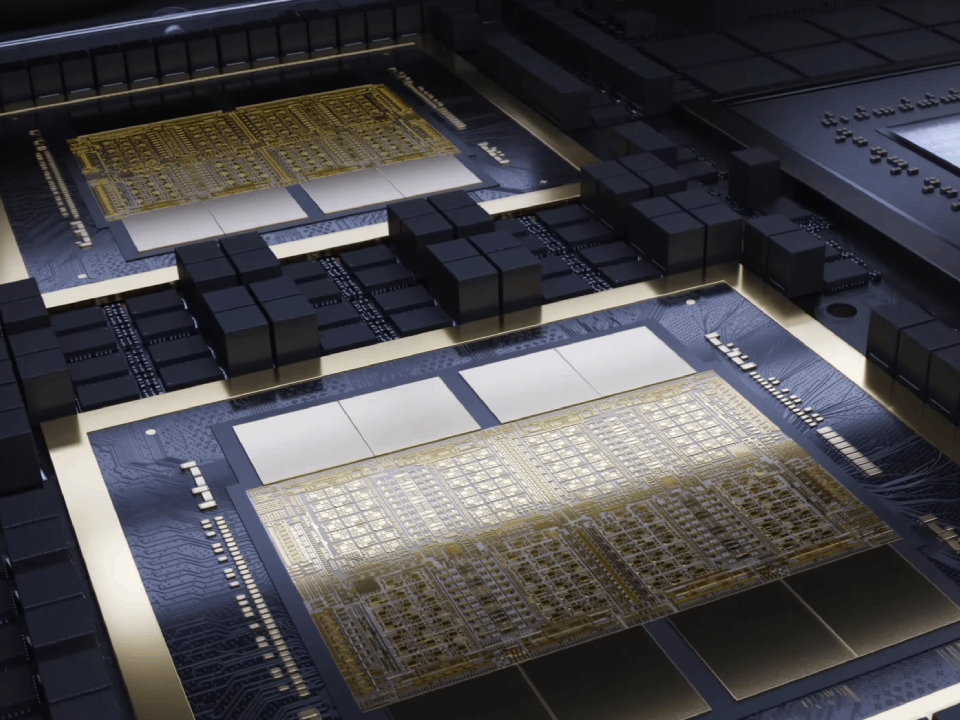

昨日、Blackwellの発表から、私がRTX 50シリーズの予想をしたのだが、早速その予想が崩された。

ま、専門家じゃないから当たり前といえば当たり前なのだが、そもそもBlackwellそのものの製造プロセスに関しても、私の認識が間違っていたようだ。

というのは、TSMCとNVIDIAでいうところの製造プロセスの命名において、一致しないらしいのである。

たとえばTSMC 4NはNVIDIAのカスタムプロセスの命名だが、TSMCの製造プロセスでいえばTSMC N5になるという。つまり、今回言われているTSMC 4NPは、単純に5nmプロセスではなく、全く別のプロセスノードになると考えられる。

具体的にどのプロセスノードなのかはまだ情報が出ていないので、具体的に半導体の密度がどれぐらいになるかはわからないというのである。

ただ、現時点で噂されている内容だと、どうもRTX 40シリーズに対して30%ほどトランジスタ密度は上昇しているらしい。

であるなら、性能もそれに準じた一定量の性能向上は果たしている可能性がある。

最近の高密度な製造プロセスでは、基板層や配線層で異なるプロセスノードを使用したりしていて複雑化している。

単純に製造プロセスと言っても、その内容は多岐にわたるため、情報が錯綜しやすいという事なのだろう。

メモリインターフェースの謎

そしてもう一つ謎がある。

それはメモリインターフェースで、少し前の噂ではメモリインターフェースはRTX 40シリーズと同等になると言われていた。つまり、最上位のRTX 4090の384bitというのが今回のRTX 50シリーズの最上位、RTX 5090、コア名でいうところのGB202でも同じく384bitが使われる、と予想されていたのだが、ここに来てGB202では512bitという話が出てきている。

また、このGB202の一つ下のコアであるGB203(おそらく5070などで使われるか?)では、GB202の半分の規模になる、という予測もあるようである。これがもし本当なら、5070系(おそらく)では256bitのメモリインターフェースという事になる。

メモリインターフェースは、RTX 40シリーズ、つまり“Ada Lovelace”では当初はRTX 4080でのみ256bitとなっていたが、今回はRTX 50シリーズが登場した直後に、ミドルレンジ以上で256bitとして登場する可能性がある。ま、GB203がどのグレードに適用されるかで変わる話ではあるが、規模をいきなり半減させたものをRTX 5080に持ってくるという事は考えにくいので、この予想はそう外れてはいないのではないかと思う。

最近のコメント